13917361033

13917361033

封装的核心设备之一,晶圆上凸点(Bump)的制作是关键技术。阐述了WLP封装工艺流程,对三种晶圆级封装凸点制作技术进行了对比。分析了WLP微球植球机工作流程

封装的核心设备之一,晶圆上凸点(Bump)的制作是关键技术。阐述了WLP封装工艺流程,对三种晶圆级封装凸点制作技术进行了对比。分析了WLP微球植球机工作流程,并对其关键技术进行了研究,包括X-Y-Z-θ植球平台、金属模板印刷和植球。最后在自主研制的半自动晶圆级微球植球机WMB-1100上进行了印刷和植球实验,通过对设备工艺

晶圆级封装(Wafer Lever Package,WLP)是以BGA技术为基础,将百微米级的焊锡球放置到刻好电路的晶圆上,是一种经过改进和提高的CSP。WLP封装具有较小封装尺寸与较佳电性表现的优势,目前多应用于轻薄短小kaiyun网站的消费性IC的封装应用。

微球植球机是晶圆级封装工艺中的必备核心设备之一。在WLP工艺中,晶圆上凸点(Bump)的制作是关键的基础技术,国内中电科技24所、华中科技大学、清华大学等单位研究了WLP封装中电镀凸点方式;哈尔滨工业大学、上海交通大学研究了激光植球技术,主要应用于BGA器件修复;合肥工业大学对BGA基板植球进行了研究。本文针对晶圆凸点制作的金属模板印刷和植球方式,研究WLP封装工艺和WLP植球机关键技术,并在自主研制的半自动晶圆级微球植球机进行植球实验,晶圆尺寸12inch,焊锡球直径250um。晶圆级植球技术和设备的开发研制为高端芯片封装装备国产化提供从技术理论到实践应用的参考。

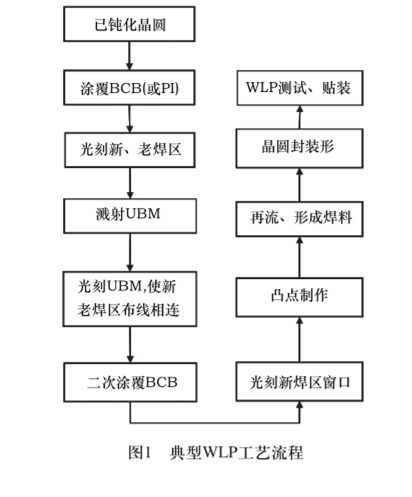

晶圆级封装,是属于芯片尺寸封装(CSP)的一种。所谓芯片尺寸封装是当芯片(Die)封装完毕后,其所占的面积小于芯片面积的120%。晶圆级封装与传统封装工艺不同,传统封装将芯片上压点和基座上标准压点连接的集成电路封装都是在由晶圆上分离出来的芯片上进行的,这种工艺造成了前端晶圆制造工艺与用于生产最终集成电路的后端装配和封装的自然分离。晶圆级封装是在在完成封装和测试后,才将晶圆按照每一个芯片的大小来进行切割,统一前端和后端工艺以减少工艺步骤,封装后的体积与IC裸芯片尺寸几乎相同,能大幅降低封装后的IC尺寸,是真正意义上的芯片尺寸封装。一片12inch的晶圆上一般有750~1500个裸片,与单个芯片封装相比,每个裸片的封装成本可以降低一个数量级。晶圆级芯片封装工艺流程如图1所示。

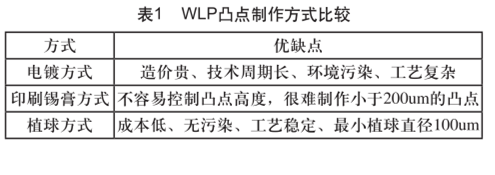

晶圆级封装采用凸点技术(Bumping)作为其I/O电极,晶圆上形成凸点有三种方式:电镀方式、印刷锡膏方式和植球方式,三种方式的比较如表1所示。

鉴于电镀方式和印刷锡膏方式的缺点,业界一直在寻找替代解决方案,晶圆级植球技术的突破恰好满足了这一需求,并且随着多层堆叠技术(MCM)的发展,要求晶圆与晶圆间具有高精度的多引脚的100um级的互联,晶圆级植球技术可以稳定地实现。

1)上料机械手对晶圆盒(Cassette)中的晶圆进行检测(Mapping);

4 )利 用超 精密 金属 模板 印刷 技术 将助 焊剂(Flux)涂敷在晶圆的焊盘上;

本次植球实验在自主研制的半自动晶圆级微球植球机进行,如图5所示。实验晶圆尺寸12inch,焊锡球直径250um。

印刷:根据刮刀长度在金属模板印刷初始位置涂抹适量助焊剂,调整刮刀气缸压强,设定为0.12MPa。CCD相机对Table上晶圆和金属模板光学定位点(Mark点)进行对中,然后执行印刷,如图6所示。

植球:植球定位与印刷定位一样,由于本次实验的12inch晶圆一次植球量多,为节省焊锡球,在晶圆上取五块具有代表性的区域,使用塑料刮板刮球,使焊锡球通过金属模板网孔落入对应晶圆上的胶点,如图7所示。

参数调整:在三次元影像测量仪上观察印刷和植球效果,如图8所示。然后进行晶圆与金属模板的X,Y,θ方向的精细调整,反复对设备的工艺参数进行调整,直到得到满意的印刷和植球效果。

经过多次印刷和植球实验,对工艺参数进行调整,最终设备的印刷和植球效果如图9、图10所示,两图分别为在三次元影像测量仪上观察到的晶圆单个裸片Die的印刷胶点和焊锡球图,误差在1/2焊锡球球径范围内。

晶圆级封装植球装备是高端IC封装的关键设备之一,封装工艺和关键技术的研究对于设备的研制十分必要。大行程、高精度植球平台是基础工作单元,完成晶圆的传送和定位,金属模板印刷和植球工艺需要长期的技术积累。通过自主研发的半自动晶圆级微球植球机WMB-1100实验,取得了良好的植球效果。晶圆级微球植球技术及装备的研制可以提高我国在高端IC封装领域的竞争力。

刘劲松 时威 张金志 (1.上海理工大学机械工程学院;2.上海微松工业自动化有限公司)

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。举报投诉

采取在芯片尺寸以外的区域做I/O接点的布线设计,提高I/O接点数量。采用RDL工艺让芯片可以使用的布线区域增加,充分利用到芯片的有效面积,达到降低成本的目的。扇出型

载板便可直接焊接在印刷线路板上,这样可以缩短信号传输距离,提高电学性能。

Wafer Level Package Technology Board Mounting Application Note for 0.800mm pitch

、应用探索及产业生态培育等方面取得诸多进展,整体发展进入快车道,已成为全球多国科研布局与投资热点。重点梳理分析量子计算

上使用双面布线工艺,实现毫米波天线阵列的制作. 将TSV转接芯片与射频芯片倒装焊在玻璃

当的方式为激光解键合。鸿浩半导体设备所生产的UV激光解键合设备具备低温、不伤

(Fan Out Wafer Level Packaging, FOWLP,简称扇出

随着超高密度多芯片模组(Multiple Chip Module,MCM)乃至系统

(SiP)产品在5G、AI、高性能运算、汽车自动驾驶等领域的普及,2.5D 和 3D

,因其具有尺寸小、电性能优良、散热好、成本低等优势,近年来发展迅速。根据Verified Market

,因其具有尺寸小、电性能优良、散热好、成本低等优势,近年来发展迅速。根据Verified Market

成为实现系统性能、带宽和功耗等方面指标提升的重要备选方案之一。对目前已有的

现像,较易控制并撑握。具体做法就是先用锡膏印刷到BGA的焊盘上,再在上面加上一定大小的锡

传苹果在2016年秋天即将推出的新款智能型手机iPhone 7(暂订)上,将搭载采用扇出型

;FOWLP)的芯片,让新iPhone更轻薄,制造成本更低。那什么是FOWLP

和具体实现。设计并实现了一种基于FFT的码相位并行的快速信号捕获方案;介绍了码跟踪环与载波跟踪环的算法流程并详细推导了伪距及精密伪距的计算过

单片机被广泛应用于工业控制,家电,消费开云网站 Kaiyun电子,医疗电子,仪表测量等领域,为应广大初级电子工程师/单片机爱好者之需,电子发烧友隆重策划整合推出《单片

单片机被广泛应用于工业控制,家电,消费电子,医疗电子,仪表测量等领域,为应广大初级电子工程师/单片机爱好者之需,电子发烧友隆重策划整合推出《单片

。文章的特色和创新点包括:1、提出了一种基于搜索矩阵的自适应防碰撞算法。算法有效地利用了碰

Copyright © 2023 开云网站有限公司 版权所有 备案号:沪ICP备15036269号